Dataflow analysis to determine which virtual registers (in high-level code) contain live values. More...

#include "live_vregs.h"

Inheritance diagram for LiveVregsAnalysis:

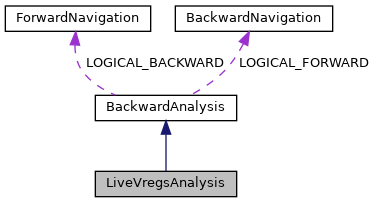

Collaboration diagram for LiveVregsAnalysis:

Public Types | |

| typedef std::bitset< MAX_VREGS > | FactType |

| Fact type is a bitset of live virtual register numbers. | |

| typedef InstructionSequence::const_reverse_iterator | InstructionIterator |

| Iterator type for iterating over instructions in a basic block in "analysis" order. | |

Public Member Functions | |

| FactType | get_top_fact () const |

| The "top" fact is an unknown value that combines nondestructively with known facts. More... | |

| FactType | combine_facts (const FactType &left, const FactType &right) const |

| Combine live sets. For this analysis, we use union. | |

| void | model_instruction (Instruction *ins, FactType &fact) const |

| Model an instruction. More... | |

| std::string | fact_to_string (const FactType &fact) const |

| Convert a dataflow fact to a string (for printing the CFG annotated with dataflow facts) More... | |

| InstructionIterator | begin (std::shared_ptr< InstructionSequence > bb) const |

| Get a begin iterator over the instructions in a basic block in "analysis" order. More... | |

| InstructionIterator | end (std::shared_ptr< InstructionSequence > bb) const |

| Get an end iterator over the instructions in a basic block in "analysis" order. More... | |

Public Attributes | |

| BackwardNavigation | LOGICAL_FORWARD |

| Logical forward navigation through the ControlFlowGraph in analysis order. | |

| ForwardNavigation | LOGICAL_BACKWARD |

| Logical backward navigation through the ControlFlowGraph in analysis order. | |

Static Public Attributes | |

| static const unsigned | MAX_VREGS = 256 |

| static const DataflowDirection | DIRECTION = DataflowDirection::BACKWARD |

| Analysis direction is backward. | |

Detailed Description

Dataflow analysis to determine which virtual registers (in high-level code) contain live values.

Member Function Documentation

◆ begin()

|

inlineinherited |

Get a begin iterator over the instructions in a basic block in "analysis" order.

- Parameters

-

bb a basic block

- Returns

- begin iterator over the instructions in the basic block

◆ end()

|

inlineinherited |

Get an end iterator over the instructions in a basic block in "analysis" order.

- Parameters

-

bb a basic block

- Returns

- end iterator over the instructions in the basic block

◆ fact_to_string()

|

inline |

Convert a dataflow fact to a string (for printing the CFG annotated with dataflow facts)

- Parameters

-

fact dataflow fact (set of virtual register numbers)

- Returns

- string representation of the dataflow fact

◆ get_top_fact()

|

inline |

The "top" fact is an unknown value that combines nondestructively with known facts.

For this analysis, it's the empty set.

◆ model_instruction()

|

inline |

Model an instruction.

- Parameters

-

ins the Instruction to model (backwards) fact initially represents what is true after the instruction (in program order), and will be updated to represent what is true before the instruction (in program order)

The documentation for this class was generated from the following file: